(2)+12V がちゃんとOFFできていない。

(3)電源OFF時、PS_ON端子に8[V]以上もの電圧が出ている。→ マザーに悪影響は?

(4)電源ON時、PS_ON端子から 12[V]/(1.2+1.2)[kΩ]=5[mA] もの電流が流れ出す。 → マザーに悪影響は?

について、もっときれいに解決する方法は何か、考えてみた。

要は、Q1のゲートを、DC-DCモジュールのOn/Off端子と単純にパラにしたため、

Q1に与える VGS にメリハリがつけられなくなっているわけである。

ならばこれらを分離してしまえばよい。そのうえでそれぞれのプルアップ抵抗値を適切に選べば、(3)(4)も改善するはず。

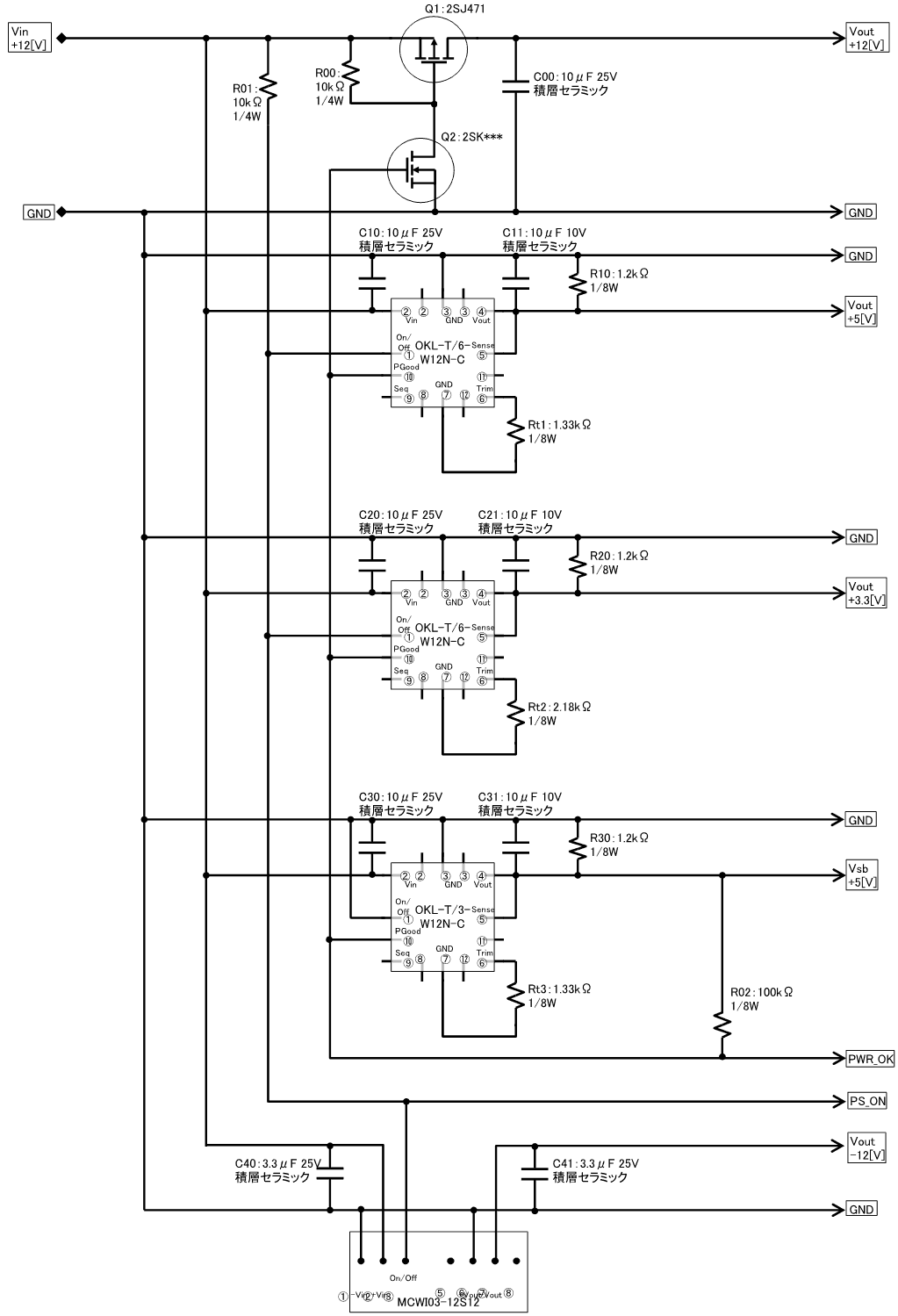

方法はいくつか考えられるが、一例として下図の回路がスマートなやり方かな、と思う。

Q2はNチャネルのMOS FET。小信号用で良いのだが、エンハンスメント型でかつ、

ゲートしきい値電圧は PWR_OK 端子の電圧 3.5[V] に対して充分低い必要がある。

これなら追加部品は FET 1個で済むから、何とかなりそうかな。

…でも気力が尽きたのでとりあえずここまで。